Code Download Features • VHDL source code of a Parity Generator component • Configurable number of input bits • Configurable selection for even or odd parity Introduction Parity evaluates whether the number of “1” bits in a binary code is odd or even. This provides a simple means of error checking. There are two types of parity with opposite results. Even parity results in a “1” if there are an odd number of “1” bits in the original code, and “0” if there are an even number.

Vhdl Program For Parity Generator Using Xor. 1/6/2018 0 Comments International Journal of Engineering Research and Applications (IJERA) is an open access online peer.

The even parity bit can be appended to the code to make the number of “1” bits even. Odd parity results in a “0” if there are an odd number of “1” bits, and “1” if there are an even number. The odd parity bit can be appended to the code to make the number of “1” bits odd. This page details a Parity Generator circuit, written in VHDL, for use in FPGAs and CPLDs.

> > > > Anyone know why steam would try to load the de_vegas texture pack when > > I'm trying to play fy_iceworld? Counter strike 1.6 iceworld map free download. > > 'Bob' wrote in message > news:1c1a941c.2c056288@posting.google.com. > > I'm running steam (CS 1.6), and every time I launch an fy_iceworld > > game, I connect to the server, download the security module, and just > > as the map is about to load, wham!, I get a Fatal Error 'Warning: > > couldn't open de_vegas.wad'. > > > > More file system info: > > C: Sierra Counter-Strike cstrike de_vegas.wad > > C: Sierra Counter-Strike cstrike maps de_vegas.bsp > > C: Sierra Counter-Strike cstrike maps de_vegas.txt > > C: Sierra Counter-Strike cstrike maps fy_iceworld.bsp > > C: Sierra Counter-Strike cstrike maps fy_iceworld.txt > > > > The last two I installed manually from a.zip file obtained from this > > website:> > > > I'm assuming there's no texture pack for fy_iceworld.right? > > > > Thanks for help.

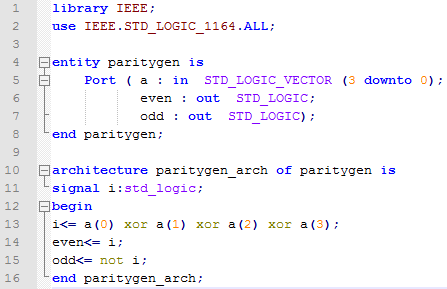

The component reads in a binary code over a parallel interface and outputs the parity bit. The size of the input code is configurable, as is whether the output parity bit is even parity or odd parity. It was designed using Quartus Prime, version 17.0.0. Theory of Operation This Parity Generator uses simple XOR logic. As the truth table in Figure 1 shows, an XOR gate outputs a ‘0’ if the number of high inputs is even and a ‘1’ if the number of high inputs is odd. XOR Truth Table.

Input A Input B Output 0 0 0 0 1 1 1 0 1 1 1 0 Figure 1 illustrates the Parity Generator. The parity_eo input makes the correction for even or odd parity, and the cascading XOR gates keep a running evaluation.

Each new gate in the series decides if the next bit in the sequence makes the running total odd or even. Once all the input bits are evaluated, the output parity presents the final result. Jo bheji thi dua mp3 song downlod.

Parity Generator Circuit Configuring the Parity Generator The Parity Generator is configured by setting the GENERIC parameters in the ENTITY. Table 2 describes the parameters. Generic Parameter Descriptions.

Latest Pages

- Obrazec Prikaza Na Provedenie Inventarizacii Tmc V Rk

- Home And Exile Chinua Achebe Pdf To Doc

- Moskovkin Russkij Yazik

- Mafia 1 Pc Game Crack Download

- Ed Friedland Building Walking Bass Lines Pdf Download Free

- Bagan Keyboard For Myanmar8723345

- Foto Payudara Besar Wanita Indah Dan Montoku

- Openbox Sx6 Hd Firmware Version

- Visshaya Matematika Uchebnik Dlya Vuzov Pdf

- Firmennij Blank Obrazec Uzbekistan